【详解】如何编写Linux下Nand Flash驱动 – 1 of 2

版本: 1.2

最后更新日期:2011-03-15

作者:crifan

邮箱:green-waste(At)163.com

——————————————————————————————-

提示:PDF版本的,可以去这里下载:

【详解】如何编写Linux下Nand Flash驱动 v1.2.pdf

http://www.rayfile.com/zh-cn/files/afd02a47-4fd3-11e0-b1d8-0015c55db73d/

http://blog.chinaunix.net/attachment/attach/77/44/27/27774427322fd7fd939212e786c1dde22b353519.pdf

——————————————————————————————-

目录

2.1.2.1. Nand Flash和Nor Flash的区别… 5

2.1.3.1. SLC(Single Level Cell)… 6

2.1.3.2. MLC(Multi Level Cell)… 6

2.1.4. Nand Flash数据存储单元的整体架构… 7

2.1.5. Nand Flash的物理存储单元的阵列组织结构… 7

2.1.5.3. oob / Redundant Area / Spare Area. 8

2.1.8. Nand Flash引脚(Pin)的说明… 8

2.1.8.2. Nand Flash只有8个I/O引脚的好处… 10

2.1.9. Nand flash的一些典型(typical)的特性… 10

2.1.10. Nand Flash控制器与Nand Flash芯片… 11

2.1.11. Nand Flash中的特殊硬件结构… 11

2.1.12. Nand Flash中的坏块(Bad Block) 11

2.1.14.1. 页编程(Page Program)注意事项… 12

2.1.14.2.2. 发送命令前的准备工作以及时序图各个信号的具体含义… 13

2.1.14.2.3. 如何计算出我们要传入的行地址和列地址… 14

2.1.15.1. 片选无关(CE don’t-care)技术… 15

2.1.15.2. 带EDC的拷回操作以及Sector的定义(Copy-Back Operation with EDC & Sector Definition for EDC) 15

2.1.15.3. 多片同时编程(Simultaneously Program Multi Plane) 15

2.1.15.4. 交错页编程(Interleave Page Program)… 15

2.1.15.5. 随机输出页内数据(Random Data Output In a Page)… 16

2.2.1. 内存技术设备,MTD(Memory Technology Device)… 16

3. Linux下Nand Flash驱动编写步骤简介… 21

图表

图表 2 Nand Flash 和 Nor Flash的区别… 5

图表 4 Nand Flash物理存储单元的阵列组织结构… 7

图表 9 Nand Flash K9K8G08U0A的命令集合… 12

图表 10 Nand Flash数据读取操作的时序图… 13

图表 13 Nand Flash数据读取操作的时序图… 16

缩略词

缩写 | 全称 |

BBM | Bad Block Management |

BBT | Bad Block Table |

EEPROM | Electrically Erasable Programmable Read-Only Memory |

MLC | Multi Level Cell |

MOSFET | Metal-Oxide -Semiconductor Field Effect Transistor 金属氧化物半导体场效应晶体管 |

SLC | Single Level Cell |

1. 正文之前

1.1. 目的

本文的主要目的是,看了之后,你应该对Nand Flash的硬件特性以及对应的Linux下软件平台有了基本的认识,进一步地,对如何实现Linux下的Nand Flash的驱动,知道要做哪些事情了,以及大概是如何实现的。这样,如果有了对应的开发环境,你就可以自己去实现Nand Flash的驱动了。

不过额外提示一句的是,写出代码,并不代表你就完全搞懂了整个系统的流程。而且已经写好的代码,很可能有bug,要你不断地调试,通过调试,你才会对整个系统以及Nand Flash的方方面面有个更深入的了解的。

而且,你会发现,为了写驱动那点代码之前,却要弄懂太多的东西,包括硬件的工作原理,软件的协议规范,软件的逻辑架构等等,最后才能去实现你的驱动,所以有人会说,你写驱动不是很简单嘛,不就是写那几行代码吗,对此,一个经典的回答就是,对于整个写驱动的工作的价值算作100元的话,写代码值1块钱,但是知道怎么写,值99块钱。^_^

1.2. 目标读者和阅读此文的前提

正因为此文目的是让你搞懂如何在Linux下面实现Nand Flash的驱动,所以,目标读者就是,希望对Nand Flash硬件知识有一定了解,和想要在Linux下面实现Nand Flash驱动的读者。

而阅读此文的前提,是要有一些基本的软硬件基础知识,和了解如何在v2.6内核之后Linux的下面开发驱动的流程。有了这些知识,再看本文,然后你才能清楚真正要去实现Nand Flash的驱动,是如何下手。

1.3. 说明

本文的逻辑是,先介绍Nand Flash的一些基本的硬件知识,然后详细分析Nand Flash的Read操作的具体的流程,清楚硬件实现的逻辑,接着介绍软件平台,即Linux下面和Nand Flash相关的内容,这样,硬件和软件都清楚是怎么回事了,然后再介绍如何去在Linux的架构下,实现Nand Flash驱动。

之前写的版本,虽然前面关于Nand Flash的内容介绍的比较详细,但是后面关于相关的MTD知识,尤其是Linux的MTD的架构和如何实现具体的Nand的Flash的操作等部分的内容,写的很简略,导致有些读者看了后,觉得是,关于如何写驱动,和没说差不多,呵呵。

因此,现在继续更新,将更详细的解释,如何从硬件Nand Flash的规范,一步步映射到具体的软件实现的过程,这样,使得读者更明白其中的内在逻辑,然后接着再介绍如何在理解了软硬件各自的所具有的功能,以及Linux的MTD系统,已经帮你实现了哪些功能,然后才会更加明白,余下的要实现的软件部分,就是你所要实现的Linux下的Nand Flash的驱动部分了。

1.4. 声明

关于此贴版权问题,欢迎转载,但是希望注明联系方式,至少其他人看到被转帖的内容,如果有疑问,建议和意见,可以及时与笔者沟通。

2. 编写驱动之前要了解的知识

2.1. 硬件特性

2.1.1.什么是Flash

Flash全名叫做Flash Memory,从名字就能看出,是种数据存储设备,存储设备有很多类,Flash属于非易失性存储设备(Non-volatile Memory Device),与此相对应的是易失性存储设备(Volatile Memory Device)。关于什么是非易失性/易失性,从名字中就可以看出,非易失性就是不容易丢失,数据存储在这类设备中,即使断电了,也不会丢失,这类设备,除了Flash,还有其他比较常见的入硬盘,ROM等,与此相对的,易失性就是断电了,数据就丢失了,比如大家常用的内存,不论是以前的SDRAM,DDR SDRAM,还是现在的DDR2,DDR3等,都是断电后,数据就没了。

2.1.1.1. Flash的硬件实现机制

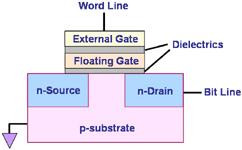

Flash的内部存储是MOSFET,里面有个悬浮门(Floating Gate),是真正存储数据的单元。

在Flash之前,紫外线可擦除(uv-erasable)的EPROM,就已经采用了Floating Gate存储数据这一技术了。

图表 1 典型的Flash内存单元的物理结构

数据在Flash内存单元中是以电荷(electrical charge) 形式存储的。存储电荷的多少,取决于图中的外部门(external gate)所被施加的电压,其控制了是向存储单元中冲入电荷还是使其释放电荷。而数据的表示,以所存储的电荷的电压是否超过一个特定的阈值Vth来表示,因此,Flash的存储单元的默认值,不是0(其他常见的存储设备,比如硬盘灯,默认值为0),而是1,而如果将电荷释放掉,电压降低到一定程度,表述数字0。

2.1.2.什么是Nand Flash

Flash主要分两种,Nand Flash和nor flash。

关于Nand Flash和Nor Flash的区别,参见【附录5】。

不过,关于两者区别,除了那个解释之外,这里再多解释解释:

1.Nor的成本相对高,容量相对小,比如常见的只有128KB,256KB,1MB,2MB等等,优点是读写数据时候,不容易出错。所以在应用领域方面,Nor Flash比较适合应用于存储少量的代码。

2.Nand flash成本相对低,说白了就是便宜,缺点是使用中数据读写容易出错,所以一般都需要有对应的软件或者硬件的数据校验算法,统称为ECC。但优点是,相对来说容量比较大,现在常见的Nand Flash都是1GB,2GB,更大的8GB的都有了,相对来说,价格便宜,因此适合用来存储大量的数据。其在嵌入式系统中的作用,相当于PC上的硬盘,用于存储大量数据。

所以,一个常见的应用组合就是,用小容量的Nor Flash存储启动代码,比如uboot,用大容量的Nand Flash做整个系统和用户数据的存储。

而一般的嵌入式平台的启动流程也就是,系统从装有启动代码的Nor Flash启动后,初始化对应的硬件,包括SDRAM等,然后将Nand Flash上的Linux 内核读取到内存中,做好该做的事情后,就跳转到SDRAM中去执行内核了,然后内核解压(如果是压缩内核的话,否则就直接运行了)后,开始运行,在Linux内核启动最后,去Nand Flash上,挂载根文件,比如jffs2,yaffs2等,挂载完成,运行初始化脚本,启动consle交互,才运行你通过console和内核交互。至此完成整个系统启动过程。

而Nor Flash就分别存放的是Uboot,Nand Flash存放的是Linux的内核镜像和根文件系统,以及余下的空间分成一个数据区。

2.1.2.1. Nand Flash和Nor Flash的区别

Nor flash,有类似于dram之类的地址总线,因此可以直接和CPU相连,CPU可以直接通过地址总线对nor flash进行访问,而Nand Flash没有这类的总线,只有IO接口,只能通过IO接口发送命令和地址,对Nand Flash内部数据进行访问。相比之下,nor flash就像是并行访问,Nand Flash就是串行访问,所以相对来说,前者的速度更快些。

但是由于物理制程/制造方面的原因,导致nor 和nand在一些具体操作方面的特性不同:

图表 2 Nand Flash 和 Nor Flash的区别

| NOR | NAND | (备注) |

接口 | 总线 | I/O接口 | 这个是两者物理结构上的最大区别 |

单个cell大小 | 大 | 小 |

|

单个Cell成本 | 高 | 低 |

|

读耗时 | 快 | 慢 |

|

单字节的编程时间 | 快 | 慢 |

|

多字节的编程时间 | 慢 | 快 |

|

擦除时间 | 慢 | 快 |

|

功耗 | 高 | 低,但是需要额外的RAM |

|

是否可以执行代码 | 是 | 不行, 但是一些新的芯片,可以在第一页之外执行一些小的loader(1) | 即是否允许,芯片内执行(XIP, eXecute In Place) (参见附录) |

位反转(Bit twiddling/bit flip) | 几乎无限制 | 1-4次,也称作 “部分页编程限制” | 也就是数据错误,0->1或1->0 |

在芯片出厂时候是否允许坏块 | 不允许 | 允许 |

|

注:

(1)理论上是可以的,而且也是有人验证过可以的,只不过由于Nand Flash的物理特性,不能完全保证所读取的数据/代码是正确的,实际上,很少这么用而已。因为,如果真是要用到Nand Flash做XIP,那么除了读出速度慢之外,还要保证有数据的校验,以保证读出来的,将要执行的代码/数据,是正确的。否则,系统很容易就跑飞了。。。

2.1.2.2. Nand Flash的详细分类

Nand Flash,按照硬件类型,可以分为

(1)Bare NAND chips:裸片,单独的Nand Flash芯片

(2)SmartMediaCards: =裸片+一层薄塑料,常用于数码相机和MP3播放器中。之所以称smart,是由于其软件smart,而不是硬件本身有啥smart之处。

(3)DiskOnChip:裸片+glue logic,glue logic=硬件ECC产生器+用于静态的nand 芯片控制的寄存器+直接访问一小片地址窗口,那块地址中包含了引导代码的stub桩,其可以从Nand Flash中拷贝真正的引导代码。

2.1.3.SLC和MLC的实现机制

Nand Flash按照内部存储数据单元的电压的不同层次,也就是单个内存单元中,是存储1位数据,还是多位数据,可以分为SLC和MLC。

2.1.3.1. SLC(Single Level Cell)

单个存储单元,只存储一位数据,表示1或0。

就是上面介绍的,对于数据的表示,单个存储单元中内部所存储电荷的电压,和某个特定的阈值电压Vth,相比,如果大于此Vth值,就是表示1,反之,小于Vth,就表示0.

对于Nand Flash的数据的写入1,就是控制External Gate去充电,使得存储的电荷够多,超过阈值Vth,就表示1了。而对于写入0,就是将其放电,电荷减少到小于Vth,就表示0了。

关于为何Nand Flash不能从0变成1,我的理解是,物理上来说,是可以实现每一位的,从0变成1的,但是实际上,对于实际的物理实现,出于效率的考虑,如果对于,每一个存储单元都能单独控制,即,0变成1就是,对每一个存储单元单独去充电,所需要的硬件实现就很复杂和昂贵,同时,所进行对块擦除的操作,也就无法实现之前所说的的,Flash的速度,即一闪而过的速度了,也就失去了Flash的众多特性了。

2.1.3.2. MLC(Multi Level Cell)

与SLC相对应的,就是单个存储单元,可以存储多个位,比如2位,4位等。其实现机制,说起来比较简单,就是通过控制内部电荷的多少,分成多个阈值,通过控制里面的电荷多少,而达到我们所需要的存储成不同的数据。比如,假设输入电压是Vin=4V(实际没有这样的电压,此处只是为了举例方便),那么,可以设计出2的2次方=4个阈值, 1/4 的Vin=1V,2/4的Vin=2V,3/4的Vin=3V,Vin=4V,分别表示2位数据00,01,10,11,对于写入数据,就是充电,通过控制内部的电荷的多少,对应表示不同的数据。

对于读取,则是通过对应的内部的电流(与Vth成反比),然后通过一系列解码电路完成读取,解析出所存储的数据。这些具体的物理实现,都是有足够精确的设备和技术,才能实现精确的数据写入和读出的。

单个存储单元可以存储2位数据的,称作2的2次方=4 Level Cell,而不是2 Level Cell,关于这点,之前看Nand flash的数据手册(datasheet)的时候,差点搞晕了。

同理,对于新出的单个存储单元可以存储4位数据的,称作 2的4次方=16 Level Cell。

2.1.3.3. 关于如何识别SLC还是MLC

Nand Flash设计中,有个命令叫做Read ID,读取ID,意思是读取芯片的ID,就像大家的身份证一样,这里读取的ID中,是读取好几个字节,一般最少是4个,新的芯片,支持5个甚至更多,从这些字节中,可以解析出很多相关的信息,比如此Nand Flash内部是几个芯片(chip)所组成的,每个chip包含了几片(Plane),每一片中的页大小,块大小,等等。在这些信息中,其中有一个,就是识别此flash是SLC还是MLC。下面这个就是最常见的Nand Flash的datasheet中所规定的,第3个字节,3rd byte,所表示的信息,其中就有SLC/MLC的识别信息:

图表 3 Nand Flash 第3个ID的含义

| Description | I/O7 | I/O6 | I/O5 I/O4 | I/O3 I/O2 | I/O1 I/O0 |

Internal Chip Number | 1 2 4 8 |

|

|

|

| 0 0 0 1 1 0 1 1 |

Cell Type | 2 Level Cell 4 Level Cell 8 Level Cell 16 Level Cell |

|

|

| 0 0 0 1 1 0 1 1 |

|

Number of Simultaneously Programmed Pages | 1 2 4 8 |

|

| 0 0 0 1 1 0 1 1 |

|

|

Interleave Program Between multiple chips | Not Support Support |

| 0 1 |

|

|

|

Cache Program | Not Support Support | 0 1 |

|

|

|

|

2.1.4.Nand Flash数据存储单元的整体架构

简单说就是,常见的Nand Flash,内部只有一个chip,每个chip只有一个plane。

而有些复杂的,容量更大的Nand Flash,内部有多个chip,每个chip有多个plane。这类的Nand Flash,往往也有更加高级的功能,比如下面要介绍的Multi Plane Program和Interleave Page Program等。

概念上,由大到小来说,就是:

Nand Flash -> Chip -> Plane -> Block -> Page -> oob

比如,型号为K9K8G08U0A这个芯片(chip),内部有两个K9F4G08U0A,每个K9F4G08U0A包含了2个Plane,每个Plane是1Gb,所以K9F4G08U0A的大小是1Gb×2=2Gb=256MB,因此,K9K8G08U0A内部有2个K9F4G08U0A,即4个Plane,总大小是4×256MB=1GB。

而型号是K9WAG08U1A的Nand Flash,内部包含了2个K9K8G08U0A,所以,总容量是K9K8G08U0A的两倍=1GB×2=2GB,类似地K9NBG08U5A,内部包含了4个K9K8G08U0A,总大小就是4×1GB=4GB。

【注意】

上面所说的block,page等Nand Flash的物理上的组织结构,是在chip的基础上来说的,但是软件编程的时候,除非你要用到Multi Plane Program和Interleave Page Program等,一般很少区分内部有几个chip以及每个chip有几个plane,而最关心的只是Nand Flash的总体容量size有多大,比如是1GB还是2GB等等。

下面详细介绍一下,Nand Flash的一个chip内部的硬件逻辑组织结构。

2.1.5.Nand Flash的物理存储单元的阵列组织结构

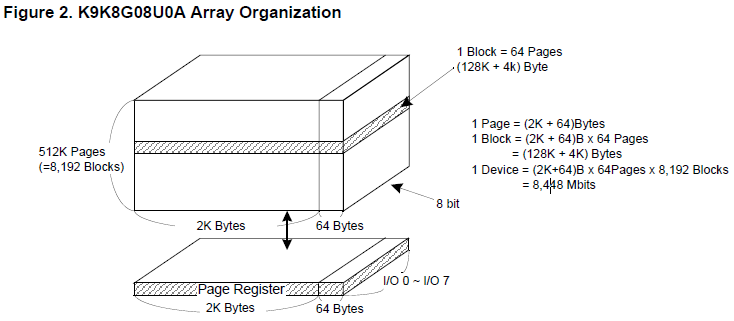

Nand Flash的内部组织结构,此处还是用图来解释,比较容易理解:

图表 4 Nand Flash物理存储单元的阵列组织结构

上图是K9K8G08U0A的datasheet中的描述。

简单解释就是:

2.1.5.1. Block块

一个Nand Flash(的chip,芯片)由很多个块(Block)组成,块的大小一般是128KB,256KB,512KB,此处是128KB。其他的小于128KB的,比如64KB,一般都是下面将要介绍到的small block的Nand Flash。

块Block,是Nand Flash的擦除操作的基本/最小单位。

2.1.5.2. Page页

每个块里面又包含了很多页(page)。每个页的大小,对于现在常见的Nand Flash多数是2KB,最新的Nand Flash的是4KB、8KB等,这类的页大小大于2KB的Nand Flash,被称作big block的Nand Flash,对应的发读写命令地址,一共5个周期(cycle),而老的Nand Flash,页大小是256B,512B,这类的Nand Flash被称作small block,地址周期只有4个。

页Page,是读写操作的基本单位。

不过,也有例外的是,有些Nand Flash支持subpage(1/2页或1/4页)子页的读写操作,不过一般很少见。

2.1.5.3. oob / Redundant Area / Spare Area

每一个页,对应还有一块区域,叫做空闲区域(spare area)/冗余区域(redundant area),而Linux系统中,一般叫做OOB(Out Of Band),这个区域,是最初基于Nand Flash的硬件特性:数据在读写时候相对容易错误,所以为了保证数据的正确性,必须要有对应的检测和纠错机制,此机制被叫做EDC(Error Detection Code)/ECC(Error Code Correction, 或者 Error Checking and Correcting),所以设计了多余的区域,用于放置数据的校验值。

Oob的读写操作,一般是随着页的操作一起完成的,即读写页的时候,对应地就读写了oob。

关于oob具体用途,总结起来有:

? 标记是否是坏快

? 存储ECC数据

? 存储一些和文件系统相关的数据。如jffs2就会用到这些空间存储一些特定信息,而yaffs2文件系统,会在oob中,存放很多和自己文件系统相关的信息。

2.1.6.Flash名称的由来

Flash的擦除操作是以block块为单位的,与此相对应的是其他很多存储设备,是以bit位为最小读取/写入的单位,Flash是一次性地擦除整个块:在发送一个擦除命令后,一次性地将一个block,常见的块的大小是128KB/256KB。。,全部擦除为1,也就是里面的内容全部都是0xFF了,由于是一下子就擦除了,相对来说,擦除用的时间很短,可以用一闪而过来形容,所以,叫做Flash Memory。所以一般将Flash翻译为 (快速)闪存。

2.1.7.Flash相对于普通设备的特殊性

根据上面提到过的,Flash最小操作单位,相对于普通存储设备,就显得有些特殊。

因为一般存储设备,比如硬盘或内存,读取和写入都是以位(bit)为单位,读取一个bit的值,将某个值写入对应的地址的位,都是可以按位操作的。

但是Flash由于物理特性,使得内部存储的数据,只能从1变成0,这点,这点可以从前面的内部实现机制了解到,对于最初始值,都是1,所以是0xFFFFFFFF,而数据的写入,即是将对应的变成0,而将数据的擦出掉,就是统一地,以block为单位,全部一起充电,所有位,都变成初始的1,而不是像普通存储设备那样,每一个位去擦除为0。而数据的写入,就是电荷放电的过程,代表的数据也从1变为了0.

所以,总结一下Flash的特殊性如下:

图表 5 Flash和普通设备相比所具有的特殊性

| 普通设备(硬盘/内存等) | Flash |

读取/写入的叫法 | 读取/写入 | 读取/编程(Program)① |

读取/写入的最小单位 | Bit/位 | Page/页 |

擦除(Erase)操作的最小单位 | Bit/位 | Block/块 ② |

擦除操作的含义 | 将数据删除/全部写入0 | 将整个块都擦除成全是1,也就是里面的数据都是0xFF ③ |

对于写操作 | 直接写即可 | 在写数据之前,要先擦除,然后再写 |

注:

① 之所以将写操作叫做编程,是因为flash是从之前的EPROM、EEPROM等继承发展而来,而之前的EEPROM,往里面写入数据,就叫做编程Program,之所以这么称呼,是因为其对数据的写入,是需要用电去擦除/写入的,所以叫做编程。

② 对于目前常见的页大小是2K/4K的Nand Flash,其块的大小有128KB/256KB/512KB等。而对于Nor Flash,常见的块大小有64K/32K等。

③在写数据之前,要先擦除,内部就都变成0xFF了,然后才能写入数据,也就是将对应的位由1变成0。

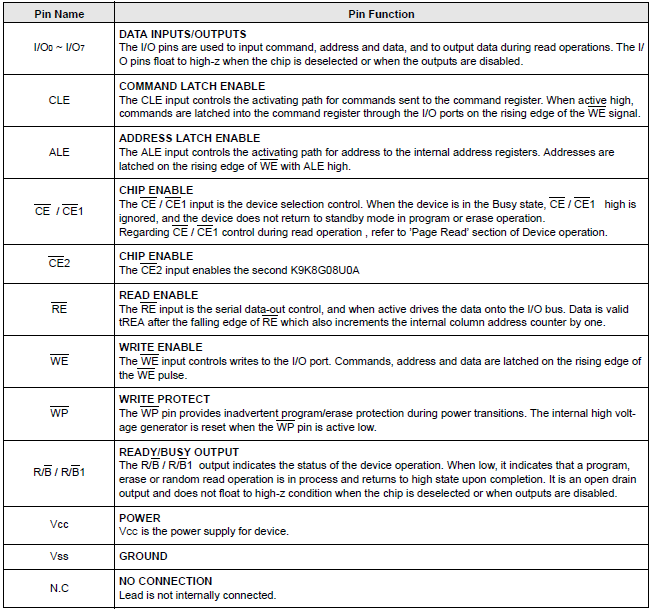

2.1.8.Nand Flash引脚(Pin)的说明

图表 6 Nand Flash引脚功能说明

上图是常见的Nand Flash所拥有的引脚(Pin)所对应的功能,简单翻译如下:

图表 7 Nand Flash引脚功能的中文说明

引脚名称 | 引脚功能 |

I/O0 ~ I/O7 | 用于输入地址/数据/命令,输出数据 |

CLE | Command Latch Enable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置CLE使能 |

ALE | Address Latch Enable,地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ALE使能 |

CE# | Chip Enable,芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作 |

RE# | Read Enable,读使能,在读取数据之前,要先使CE#有效。 |

WE# | Write Enable,写使能, 在写取数据之前,要先使WE#有效 |

WP# | Write Protect,写保护 |

R/B# | Ready/Busy Output,就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成 |

Vcc | Power,电源 |

Vss | Ground,接地 |

N.C | Non-Connection,未定义,未连接 |

【小常识】

在数据手册中,你常会看到,对于一个引脚定义,有些字母上面带一横杠的,那是说明此引脚/信号是低电平有效,比如你上面看到的RE头上有个横线,就是说明,此RE是低电平有效,此外,为了书写方便,在字母后面加“#”,也是表示低电平有效,比如我上面写的CE#;如果字母头上啥都没有,就是默认的高电平有效,比如上面的CLE,就是高电平有效。

2.1.8.1. 为何需要ALE和CLE

硬件上,有了电源的Vcc和接地的Vss等引脚,很好理解,但是为何还要有ALE和CLE这样的引脚,为何设计这么多的命令,把整个系统搞这么复杂,关于这点,最后终于想明白了:

设计命令锁存使能(Command Latch Enable, CLE) 和 地址锁存使能(Address Latch Enable,ALE),那是因为,Nand Flash就8个I/O,而且是复用的,也就是,可以传数据,也可以传地址,也可以传命令,为了区分你当前传入的到底是啥,所以,先要用发一个CLE(或ALE)命令,告诉Nand Flash的控制器一声,我下面要传的是命令(或地址),这样,里面才能根据传入的内容,进行对应的动作。否则,Nand Flash内部,怎么知道你传入的是数据,还是地址,还是命令,也就无法实现正确的操作了.

2.1.8.2. Nand Flash只有8个I/O引脚的好处

在Nand Flash的硬件设计中,你会发现很多个引脚。关于硬件上为何设计这样的引脚,而不是直接像其他存储设备,比如普通的RAM,直接是一对数据线引出来,多么方便和好理解啊。

关于这样设计的好处:

2.1.8.2.1. 减少外围连线:

相对于并口(Parellel)的Nor Flash的48或52个引脚来说,的确是大大减小了引脚数目,这样封装后的芯片体积,就小很多。现在芯片在向体积更小,功能更强,功耗更低发展,减小芯片体积,就是很大的优势。同时,减少芯片接口,也意味着使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

2.1.8.2.2. 提高系统的可扩展性

因为没有像其他设备一样用物理大小对应的完全数目的addr引脚,在芯片内部换了芯片的大小等的改动,对于用全部的地址addr的引脚,那么就会引起这些引脚数目的增加,比如容量扩大一倍,地址空间/寻址空间扩大一倍,所以,地址线数目/addr引脚数目,就要多加一个,而对于统一用8个I/O的引脚的Nand Flash,由于对外提供的都是统一的8个引脚,内部的芯片大小的变化或者其他的变化,对于外部使用者(比如编写Nand Flash驱动的人)来说,不需要关心,只是保证新的芯片,还是遵循同样的接口,同样的时序,同样的命令,就可以了。这样就提高了系统的扩展性。

说白了,对于旧的Nand Flash所实现的驱动,这些软件工作,在换新的硬件的Nand Flash的情况下,仍然可以工作,或者是通过极少的修改,就同样可以工作,使得软硬件兼容性大大提高。

2.1.9.Nand flash的一些典型(typical)的特性

1. 页擦除时间是200us,有些慢的有800us。

2. 块擦除时间是1.5ms.

3. 页数据读取到数据寄存器的时间一般是20us。

4. 串行访问(Serial access)读取一个数据的时间是25ns,而一些旧的Nand Flash是30ns,甚至是50ns。

5. 输入输出端口是地址和数据以及命令一起multiplex复用的。

6. Nand Flash的编程/擦除的寿命:即,最多允许的擦除的次数。

以前老的Nand Flash,编程/擦除时间比较短,比如K9G8G08U0M,才5K次,而后来的多数也只有10K=1万次,而现在很多新的Nand Flash,技术提高了,比如,Micron的MT29F1GxxABB,Numonyx的 NAND04G-B2D/NAND08G-BxC,都可以达到100K,也就是10万次的编程/擦除,达到和接近于之前常见的Nor Flash,几乎是同样的使用寿命了。

7. 封装形式:48引脚的TSOP1封装 或 52引脚的ULGA封装

下转:

【详解】如何编写Linux下Nand Flash驱动 – 2 of 2

http://againinput4.blog.163.com/blog/static/172799491201121691539826/

你写得确实很好,不过太多了,文字表述自我太繁琐,我觉得要简介一点比较容易看懂,我看了是似是而非,不过真的谢谢你!我的建议就是写一些实用性比较强的,操作性比较强的,可以写一个简化版!

**>> Block 621 needs retiring

yaffs: Failed to mark bad and erase block 621

**>> Block 621 retired

**>> Block 622 needs retiring

yaffs: Failed to mark bad and erase block 622

**>> Block 622 retired

**>> Block 623 needs retiring

yaffs: Failed to mark bad and erase block 623

**>> Block 623 retired

**>> Block 624 needs retiring

yaffs: Failed to mark bad and erase block 624

**>> Block 624 retired

**>> Block 625 needs retiring

yaffs: Failed to mark bad and erase block 625

**>> Block 625 retired

**>> Block 626 needs retiring

yaffs: Failed to mark bad and erase block 626

**>> Block 626 retired

**>> Block 627 needs retiring

yaffs: Failed to mark bad and erase block 627

**>> Block 627 retired

RomBOOTock 628 needs retiring

Start AT91Bootstrap...

太简洁,就起不到介绍作用了。

不过对于只是想要了解Linux下编程的,可以自己跳过前面的介绍,直接看后面的内容。

关于实用性较强的,最新版本里面,代码方面的内容会稍微多点,也更实用点。

感兴趣可以去看看:

【详解】如何编写Linux下Nand Flash驱动 v1.8

http://bbs.chinaunix.net/thread-3603541-1-1.html