提示:PDF版本的,可以去这里下载:

【详解】如何编写Linux下Nand Flash驱动 v1.2.pdf

http://www.rayfile.com/zh-cn/files/afd02a47-4fd3-11e0-b1d8-0015c55db73d/

http://blog.chinaunix.net/attachment/attach/77/44/27/27774427322fd7fd939212e786c1dde22b353519.pdf

————————————————————————————————

上接:

【详解】如何编写Linux下Nand Flash驱动 – 1 of 2

http://againinput4.blog.163.com/blog/static/17279949120112169055495/

【详解】如何编写Linux下Nand Flash驱动 – 2 of 2

版本: 1.2

最后更新日期:2011-03-15

作者:crifan

邮箱:green-waste(At)163.com

2.1.11. Nand Flash中的特殊硬件结构

由于Nand Flash相对其他常见设备来说,比较特殊,所以,特殊的设备,就有特殊的设计,就对应某些特殊的硬件特性,就有必要解释解释:

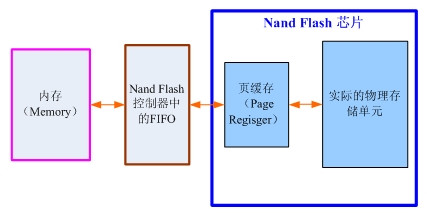

页寄存器(Page Register):由于Nand Flash读取和编程操作来说,一般最小单位是页,所以Nand Flash在硬件设计时候,就考虑到这一特性,对于每一片(Plane),都有一个对应的区域专门用于存放,将要写入到物理存储单元中去的或者刚从存储单元中读取出来的,一页的数据,这个数据缓存区,本质上就是一个缓存buffer,但是只是此处datasheet里面把其叫做页寄存器page register而已,实际将其理解为页缓存,更贴切原意。

而正是因为有些人不了解此内部结构,才容易产生之前遇到的某人的误解,以为内存里面的数据,通过Nand Flash的FIFO,写入到Nand Flash里面去,就以为立刻实现了实际数据写入到物理存储单元中了,而实际上只是写到了这个页缓存中,只有当你再发送了对应的编程第二阶段的确认命令,即0x10,之后,实际的编程动作才开始,才开始把页缓存中的数据,一点点写到物理存储单元中去。

所以,简单总结一下就是,对于数据的流向,实际是经过了如下步骤:

图表 8 Nand Flash读写时的数据流向

2.1.12. Nand Flash中的坏块(Bad Block)

Nand Flash中,一个块中含有1个或多个位是坏的,就称为其为坏块Bad Block。

坏块的稳定性是无法保证的,也就是说,不能保证你写入的数据是对的,或者写入对了,读出来也不一定对的。与此对应的正常的块,肯定是写入读出都是正常的。

2.1.12.1. 坏块的分类

坏块有两种:

(1) 出厂时就有存在的坏块:

一种是出厂的时候,也就是,你买到的新的,还没用过的Nand Flash,就可以包含了坏块。此类出厂时就有的坏块,被称作factory (masked) bad block或initial bad/invalid block,在出厂之前,就会做对应的标记,标为坏块。

(2) 使用过程中产生的坏块:

第二类叫做在使用过程中产生的,由于使用过程时间长了,在擦块除的时候,出错了,说明此块坏了,也要在程序运行过程中,发现,并且标记成坏块的。具体标记的位置,和上面一样。这类块叫做worn-out bad block。即用坏了的块。

2.1.12.2. 坏块的标记

具体标记的地方是,对于现在常见的页大小为2K的Nand Flash,是块中第一个页的oob起始位置(关于什么是页和oob,下面会有详细解释)的第1个字节(旧的小页面,pagesize是512B甚至256B的Nand Flash,坏块标记是第6个字节),如果不是0xFF,就说明是坏块。相对应的是,所有正常的块,好的块,里面所有数据都是0xFF的。

不过,对于现在新出的有些Nand Flash,很多标记方式,有些变化,有的变成该坏块的第一个页或者第二个页,也有的是,倒数最后一个或倒数第二个页,用于标记坏块的。

具体的信息,请参考对应的Nand Flash的数据手册,其中会有说明。

< xmlnamespace prefix =”o” ns =”urn:schemas-microsoft-com:office:office” />

对于坏块的标记,本质上,也只是对应的flash上的某些字节的数据是非0xFF而已,所以,只要是数据,就是可以读取和写入的。也就意味着,可以写入其他值,也就把这个坏块标记信息破坏了。对于出厂时的坏块,一般是不建议将标记好的信息擦除掉的。

uboot中有个命令是“nand scrub”就可以将块中所有的内容都擦除了,包括坏块标记,不论是出厂时的,还是后来使用过程中出现而新标记的。一般来说,不建议用这个。

不过,在实际的驱动编程开发过程中,为了方便起见,我倒是经常用,其实也没啥大碍,呵呵。不过呢,其实最好的做法是,用“nand erase”只擦除好的块,对于已经标记坏块的块,不要轻易擦除掉,否则就很难区分哪些是出厂时就坏的,哪些是后来使用过程中用坏的了。

2.1.12.3. 坏块的管理

对于坏块的管理,在Linux系统中,叫做坏块管理(BBM,Bad Block Management),对应的会有一个表去记录好块,坏块的信息,以及坏块是出厂就有的,还是后来使用产生的,这个表叫做坏块表(BBT,Bad Block Table)。在Linux 内核MTD架构下的Nand Flash驱动,和Uboot中Nand Flash驱动中,在加载完驱动之后,如果你没有加入参数主动要求跳过坏块扫描的话,那么都会去主动扫描坏块,建立必要的BBT的,以备后面坏块管理所使用。

2.1.12.4. 坏块的比例

而关于好块和坏块,Nand Flash在出厂的时候,会做出保证:

1.关于好的,可以使用的块的数目达到一定的数目,比如三星的K< xmlnamespace prefix =”st1″ ns =”urn:schemas-microsoft-com:office:smarttags” />9G8G08U0M,整个flash一共有4096个块,出厂的时候,保证好的块至少大于3996个,也就是意思是,你新买到这个型号的Nand Flash,最坏的可能, 有3096-3996=100个坏块。不过,事实上,现在出厂时的坏块,比较少,绝大多数,都是使用时间长了,在使用过程中出现的。

2.保证第一个块是好的,并且一般相对来说比较耐用。做此保证的主要原因是,很多Nand Flash坏块管理方法中,就是将第一个块,用来存储上面提到的BBT,否则,都是出错几率一样的块,那么也就不太好管理了,连放BBT的地方,都不好找了,^_^。

一般来说,不同型号的Nand Flash的数据手册中,也会提到,自己的这个Nand Flash,最多允许多少个坏块。就比如上面提到的,三星的K9G8G08U0M,最多有100个坏块。

2.1.13. Nand Flash中页的访问顺序

在一个块内,对每一个页进行编程的话,必须是顺序的,而不能是随机的。比如,一个块中有128个页,那么你只能先对page0编程,再对page1编程,。。。。,而不能随机的,比如先对page3,再page1,page2.,page0,page4,。。。

2.1.14. 常见的Nand Flash的操作

要实现对Nand Flash的操作,比如读取一页的数据,写入一页的数据等,都要发送对应的命令,而且要符合硬件的规定,如图:

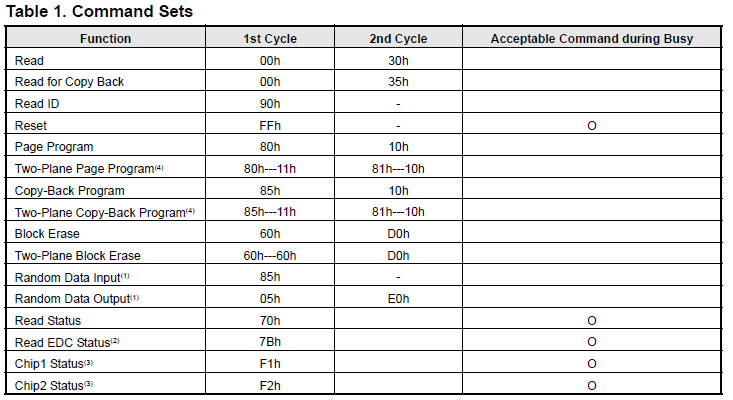

图表 9 Nand Flash K9K8G08U0A的命令集合

从上图可以看到,如果要实现读一个页的数据,就要发送Read的命令,而且是分两个周期(Cycle),即分两次发送对应的命令,第一次是0x00h,第二次是0x30h,而两次命令中间,需要发送对应的你所要读取的页的地址,关于此部分详细内容,留待后表。

对应地,其他常见的一些操作,比如写一个页的数据(Page Program),就是先发送0x80h,然后发生要写入的地址,再发送0x10h。

【提示】

对于不同厂家的不同型号的Nand Flash 的基本操作,即读页数据Read Page,写页数据(对页进行编程)Page Program,擦除整个块的数据Erase Block等操作,所用的命令都是一样的,但是针对一些Nand Flash的高级的一些特性,比如交错页编程(Interleave Page Program),多片同时编程(Simultaneously Program Multi Plane)等,所用的命令,未必一样,不过对于同一厂家的Nand Flash的芯片,那一般来说,都是统一的。

关于一些常见的操作,比如读一个页的Read操作和写一个页的Page Program,下面开始更深入的介绍。

2.1.14.1. 页编程(Page Program)注意事项

Nand flash的写操作叫做编程Program,编程,一般情况下,是以页为单位的。

有的Nand Flash,比如K9K8G08U0A,支持部分页编程(Partial Page Program),但是有一些限制:在同一个页内的,连续的部分页的编程,不能超过4次。

一般情况下,都是以页为单位进行编程操作的,很少使用到部分页编程。

关于这个部分页编程,本来是一个页的写操作,却用两个命令或更多的命令去实现,看起来是操作多余,效率不高,但是实际上,有其特殊考虑:

至少对于块擦除来说,开始的命令0x60是擦除设置命令(erase setup comman),然后传入要擦除的块地址,然后再传入擦除确认命令(erase confirm command)0xD0,以开始擦除的操作。

这种完成单个操作要分两步发送命令的设计,即先开始设置,再最后确认的命令方式,是为了避免由于外部由于无意的/未预料而产生的噪音,比如,由于某种噪音,而产生了0x60命令,此时,即使被Nand Flash误认为是擦除操作,但是没有之后的确认操作0xD0,Nand Flash就不会去擦除数据,这样使得数据更安全,不会由于噪音而误操作。

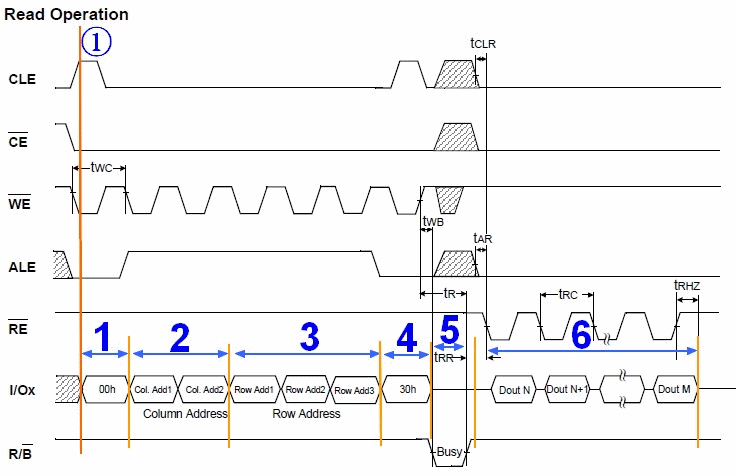

2.1.14.2. 读(Read)操作过程详解

下面以最简单的read操作为例,解释如何理解时序图,以及将时序图中的要求,转化为代码。

解释时序图之前,让我们先要搞清楚,我们要做的事情:

从Nand Flash的某个页Page里面,读取我们要的数据。

要实现此功能,会涉及到几部分的知识,即使我们不太懂Nand Flash的细节,但是通过前面的基本知识的介绍,那么以我们的常识,至少很容易想到的就是,需要用到哪些命令,怎么发这些命令,怎么计算所需要的地址,怎么读取我们要的数据等等。

下面就一步步的解释,需要做什么,以及如何去做:

2.1.14.2.1. 需要使用何种命令

首先,是要了解,对于读取数据,要用什么命令:

根据前面关于Nand Flash的命令集合介绍,我们知道,要读取数据,要用到Read命令,该命令需要2个周期,第一个周期发0x00,第二个周期发0x30。

2.1.14.2.2. 发送命令前的准备工作以及时序图各个信号的具体含义

知道了用何命令后,再去了解如何发送这些命令。

【小常识】

在开始解释前,关于”使能”这个词要罗嗦一下,以防有些读者和我以前一样,在听这类词语的时候,属于初次接触,或者接触不多的,就很容易被搞得一头雾水的(虽然该词汇对于某些专业人士说是属于最基本的词汇了,囧)。

使能(Enable),是指使其(某个信号)有效,使其生效的意思,“使其”“能够”怎么怎么样。。。。比如,上面图中的CLE线号,是高电平有效,如果此时将其设为高电平,我们就叫做,将CLE使能,也就是使其生效的意思。

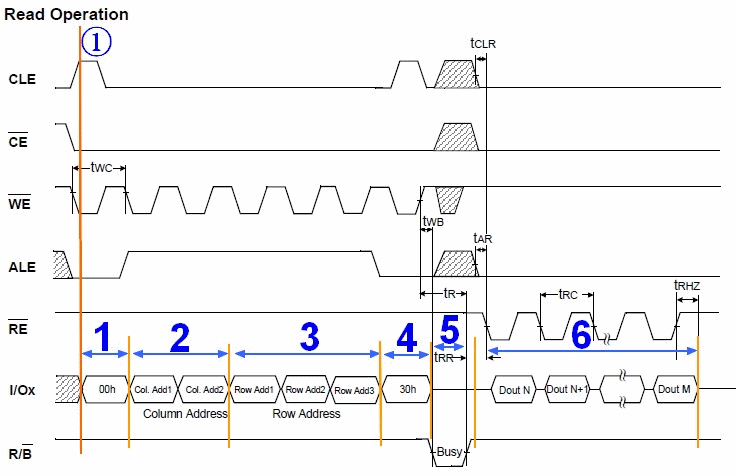

图表 10 Nand Flash数据读取操作的时序图

注:此图来自三星的型号K9K8G08U0A的Nand Flash的数据手册(datasheet)。

我们来一起看看,我在图6中的特意标注的①边上的黄色竖线。

黄色竖线所处的时刻,是在发送读操作的第一个周期的命令0x00之前的那一刻。

让我们看看,在那一刻,其所穿过好几行都对应什么值,以及进一步理解,为何要那个值。

(1)黄色竖线穿过的第一行,是CLE。还记得前面介绍命令所存使能(CLE)那个引脚吧?CLE,将CLE置1,就说明你将要通过I/O复用端口发送进入Nand Flash的,是命令,而不是地址或者其他类型的数据。只有这样将CLE置1,使其有效,才能去通知了内部硬件逻辑,你接下来将收到的是命令,内部硬件逻辑,才会将受到的命令,放到命令寄存器中,才能实现后面正确的操作,否则,不去将CLE置1使其有效,硬件会无所适从,不知道你传入的到底是数据还是命令了。

(2)而第二行,是CE#,那一刻的值是0。这个道理很简单,你既然要向Nand Flash发命令,那么先要选中它,所以,要保证CE#为低电平,使其有效,也就是片选有效。

(3)第三行是WE#,意思是写使能。因为接下来是往Nand Flash里面写命令,所以,要使得WE#有效,所以设为低电平。

(4)第四行,是ALE是低电平,而ALE是高电平有效,此时意思就是使其无效。而对应地,前面介绍的,使CLE有效,因为将要数据的是命令(此时是发送图示所示的读命令第二周期的0x30),而不是地址。如果在其他某些场合,比如接下来的要输入地址的时候,就要使其有效,而使CLE无效了。

(5)第五行,RE#,此时是高电平,无效。可以看到,知道后面低6阶段,才变成低电平,才有效,因为那时候,要发生读取命令,去读取数据。

(6)第六行,就是我们重点要介绍的,复用的输入输出I/O端口了,此刻,还没有输入数据,接下来,在不同的阶段,会输入或输出不同的数据/地址。

(7)第七行,R/B#,高电平,表示R(Ready)/就绪,因为到了后面的第5阶段,硬件内部,在第四阶段,接受了外界的读取命令后,把该页的数据一点点送到页寄存器中,这段时间,属于系统在忙着干活,属于忙的阶段,所以,R/B#才变成低,表示Busy忙的状态的。

介绍了时刻①的各个信号的值,以及为何是这个值之后,相信,后面的各个时刻,对应的不同信号的各个值,大家就会自己慢慢分析了,也就容易理解具体的操作顺序和原理了。

2.1.14.2.3. 如何计算出我们要传入的行地址和列地址

在介绍具体读取数据的详细流程之前,还要做一件事,那就是,先要搞懂我们要访问的地址,以及这些地址,如何分解后,一点点传入进去,使得硬件能识别才行。

此处还是以K9K8G08U0A为例,此Nand Flash,一共有8192个块,每个块内有64页,每个页是2K+64 Bytes,假设,我们要访问其中的第7000个块中的第25页中的1208字节处的地址,此时,我们就要先把具体的地址算出来:

物理地址

=块大小×块号+页大小×页号+页内地址

=7000×128K+64×2K+1208

=0x36B204B8,

接下来,我们就看看,怎么才能把这个实际的物理地址,转化为Nand Flash所要求的格式。

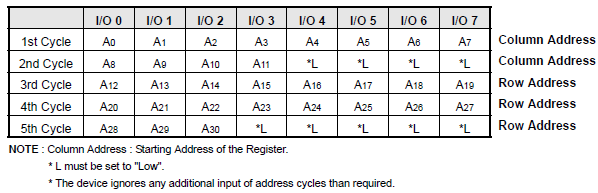

在解释地址组成之前,先要来看看其datasheet中关于地址周期的介绍:

图表 11 Nand Flash的地址周期组成

结合图7和图5中的2,3阶段,我们可以看出,此Nand Flash地址周期共有5个,2个列(Column)周期,3个行(Row)周期。而对于对应地,我们可以看出,实际上,列地址A0~A10,就是页内地址,地址范围是从0到2047,而对出的A11,理论上可以表示2048~4095,但是实际上,我们最多也只用到了2048~2011,用于表示页内的oob区域,其大小是64字节。

对应地,A12~A30,称作页号,页的号码,可以定位到具体是哪一个页。而其中,A18~A30,表示对应的块号,即属于哪个块。

简单解释完了地址组成,那么就很容易分析上面例子中的地址了:

0x36B204B8 = 0011 0110 1011 0010 0000 0100 1011 1000,分别分配到5个地址周期就是:

1st 周期,A7~A0 :1011 1000 = 0x B8

2nd周期,A11~A8 :0000 0100 = 0x04

3rd周期,A19~A12 :0010 0000 = 0x20

4th周期,A27~A20 :0110 1011 = 0x6B

5th周期,A30~A28 :0000 0011 = 0x03

注意,与图7中对应的,*L,意思是地电平,由于未用到那些位,datasheet中强制要求设为0,所以,才有上面的2nd周期中的高4位是0000.其他的A30之后的位也是类似原理,都是0。

因此,接下来要介绍的,我们要访问第7000个块中的第25页中的1208字节处的话,所要传入的地址就是分5个周期,分别传入两个列地址的:0xB8,0x04,然后再传3个行地址的:0x20,0x6B,0x03,这样硬件才能识别。

2.1.14.2.4. 读操作过程的解释

准备工作终于完了,下面就可以开始解释说明,对于读操作的,上面图中标出来的,1-6个阶段,具体是什么含义。

操作准备阶段:此处是读(Read)操作,所以,先发一个图5中读命令的第一个阶段的0x00,表示,让硬件先准备一下,接下来的操作是读。

发送两个周期的列地址。也就是页内地址,表示,我要从一个页的什么位置开始读取数据。

接下来再传入三个行地址。对应的也就是页号。

然后再发一个读操作的第二个周期的命令0x30。接下来,就是硬件内部自己的事情了。

Nand Flash内部硬件逻辑,负责去按照你的要求,根据传入的地址,找到哪个块中的哪个页,然后把整个这一页的数据,都一点点搬运到页缓存中去。而在此期间,你所能做的事,也就只需要去读取状态寄存器,看看对应的位的值,也就是R/B#那一位,是1还是0,0的话,就表示,系统是busy,仍在”忙“(着读取数据),如果是1,就说系统活干完了,忙清了,已经把整个页的数据都搬运到页缓存里去了,你可以接下来读取你要的数据了。

对于这里。估计有人会问了,这一个页一共2048+64字节,如果我传入的页内地址,就像上面给的1208一类的值,只是想读取1028到2011这部分数据,而不是页开始的0地址整个页的数据,那么内部硬件却读取整个页的数据出来,岂不是很浪费吗?答案是,的确很浪费,效率看起来不高,但是实际就是这么做的,而且本身读取整个页的数据,相对时间并不长,而且读出来之后,内部数据指针会定位到你刚才所制定的1208的那个位置。

接下来,就是你“窃取“系统忙了半天之后的劳动成果的时候了,呵呵。通过先去Nand Flash的控制器中的数据寄存器中写入你要读取多少个字节(byte)/字(word),然后就可以去Nand Flash的控制器的FIFO中,一点点读取你要的数据了。

至此,整个Nand Flash的读操作就完成了。

对于其他操作,可以根据我上面的分析,一点点自己去看datasheet,根据里面的时序图去分析具体的操作过程,然后对照代码,会更加清楚具体是如何实现的。

2.1.15. Nand Flash的一些高级特性

2.1.15.1. 片选无关(CE don’t-care)技术

很多Nand flash支持一个叫做CE don’t-care的技术,字面意思就是,不关心是否片选。

对此也许有人会问了,如果不片选,那还能对其操作吗?答案就是,这个技术,主要用在当时是不需要选中芯片,但是芯片内部却仍可以继续操作的这些情况:在某些应用,比如录音,音频播放等应用中,外部使用的微秒(us)级的时钟周期,此处假设是比较少的2us,在进行读取一页或者对页编程时,是对Nand Flash操作,这样的串行(Serial Access)访问的周期都是20/30/50ns,都是纳秒(ns)级的,此处假设是50ns,当你已经发了对应的读或写的命令之后,接下来只是需要Nand Flash内部去自己操作,将数据读取除了或写入进去到内部的数据寄存器中而已,此处,如果可以把片选取消,CE#是低电平有效,取消片选就是拉高电平,这样会在下一个外部命令发送过来之前,即微秒量级的时间里面,即2us-50ns≈2us,这段时间的取消片选,可以降低很少的系统功耗,但是多次的操作,就可以在很大程度上降低整体的功耗了。

总的来说就是:由于某些外部应用所需要的访问Nand Flash的频率比较低,而Nand Flash内部操作速度比较快,所以在针对Nand Flash的读或写操作的大部分时间里面,都是在等待外部命令的输入,同时却选中芯片,产生了多余的功耗,此“不关心片选”技术,就是在Nand Flash的内部的相对快速的操作(读或写)完成之后,就取消片选,以节省系统功耗。待下次外部命令/数据/地址输入来的时候,再选中芯片,即可正常继续操作了。这样,整体上,就可以大大降低系统功耗了。

【提示】

1. 如果想要操作硬件Nand Flash芯片,先要将对应的CE#(低有效)片选信号拉低,选中该芯片,然后才能做接下来的读写操作所要做的发命令,发数据等动作。

2.Nand Flash的片选与否,功耗差别会有很大。如果数据没有记错的话,我之前遇到我们系统里面的Nand Flash的片选,大概有5个mA的电流输出呢,也许你对5mA没太多概念,给你说个数据你就知道了:当时为了针对MP3播放功耗进行优化,整个系统优化之后的待机功耗,也才10个mA左右的,所以节省5mA已经算是很不错的功耗优化了。

2.1.15.2. 带EDC的拷回操作以及Sector的定义(Copy-Back Operation with EDC & Sector Definition for EDC)

Copy-Back功能,简单的说就是,将一个页的数据,拷贝到另一个页。

如果没有Copy-Back功能,那么正常的做法就是,先要将那个页的数据拷贝出来放到内存的数据buffer中,读出来之后,再用写命令将这页的数据,写到新的页里面。

而Copy-Back功能的好处在于,不需要用到外部的存储空间,不需要读出来放到外部的buffer里面,而是可以直接读取数据到内部的页寄存器(page register)然后写到新的页里面去。而且,为了保证数据的正确,要硬件支持EDC(Error Detection Code)的,否则,在数据的拷贝过程中,可能会出现错误,并且拷贝次数多了,可能会累积更多错误。

而对于错误检测来说,硬件一般支持的是512字节数据,对应有16字节用来存放校验产生的ECC数值,而这512字节一般叫做一个扇区。对于2K+64字节大小的页来说,按照512字节分,分别叫做A,B,C,D区,而后面的64字节的oob区域,按照16字节一个区,分别叫做E,F,G,H区,对应存放A,B,C,D数据区的ECC的值。

Copy-Back编程的主要作用在于,去掉了数据串行读取出来,再串行写入进去的时间,所以,而这部分操作,是比较耗时的,所以此技术可以提高编程效率,提高系统整体性能。

2.1.15.3. 多片同时编程(Simultaneously Program Multi Plane)

对于有些新出的Nand Flash,支持同时对多个片进行编程,比如上面提到的三星的K9K8G08U0A,内部包含4片(Plane),分别叫做Plane0,Plane1,Plane2,Plane3。.由于硬件上,对于每一个Plane,都有对应的大小是2048+64=2112字节的页寄存器(Page Register),使得同时支持多个Plane编程成为可能。 K9K8G08U0A支持同时对2个Plane进行编程。不过要注意的是,只能对Plane0和Plane1或者Plane2和Plane3,同时编程,而不支持Plane0和Plane2同时编程。

2.1.15.4. 交错页编程(Interleave Page Program)

多片同时编程,是针对一个chip里面的多个Plane来说的,

而此处的交错页编程,是指对多个chip而言的。

可以先对一个chip,假设叫chip1,里面的一页进行编程,然后此时,chip1内部就开始将数据一点点写到页里面,就出于忙的状态了,而此时可以利用这个时间,对出于就绪状态的chip2,也进行页编程,发送对应的命令后,chip2内部也就开始慢慢的写数据到存储单元里面去了,也出于忙的状态了。此时,再去检查chip1,如果编程完成了,就可以开始下一页的编程了,然后发完命令后,就让其内部慢慢的编程吧,再去检查chip2,如果也是编程完了,也就可以进行接下来的其他页的编程了。如此,交互操作chip1和chip2,就可以有效地利用时间,使得整体编程效率提高近2倍,大大提高Nand Flash的编程/擦写速度了。

2.1.15.5. 随机输出页内数据(Random Data Output In a Page)

在介绍此特性之前,先要说说,与Random Data Output In a Page相对应的是,普通的,正常的,sequential data output in a page。

正常情况下,我们读取数据,都是先发读命令,然后等待数据从存储单元到内部的页数据寄存器中后,我们通过不断地将RE#(Read Enale,低电平有效)置低,然后从我们开始传入的列的起始地址,一点点读出我们要的数据,直到页的末尾,当然有可能还没到页地址的末尾,就不再读了。所谓的顺序(sequential)读取也就是,根据你之前发送的列地址的起始地址开始,每读一个字节的数据出来,内部的数据指针就加1,移到下个字节的地址,然后你再读下一个字节数据,就可以读出来你要的数据了,直到读取全部的数据出来为止。

而此处的随机(random)读取,就是在你正常的顺序读取的过程中,先发一个随机读取的开始命令0x05命令,再传入你要将内部那个数据指针定位到具体什么地址,也就是2个cycle的列地址,然后再发随机读取结束命令0xE0,然后,内部那个数据地址指针,就会移动到你所制定的位置了,你接下来再读取的数据,就是从那个制定地址开始的数据了。

而Nand Flash数据手册里面也说了,这样的随机读取,你可以多次操作,没限制的。

请注意,上面你所传入的地址,都是列地址,也就是页内地址,也就是说,对于页大小为2K的Nand Flash来说,所传入的地址,应该是小于2048+64=2112的。

不过,实际在Nand Flash的使用中,好像这种用法很少的。绝大多数,都是顺序读取数据。

2.2. 软件方面

如果想要在Linux下编写Nand Flash驱动,那么就先要搞清楚Linux下,关于此部分的整个框架。弄明白,系统是如何管理你的Nand Flash的,以及,系统都帮你做了那些准备工作,而剩下的,驱动底层实现部分,你要去实现哪些功能,才能使得硬件正常工作起来。

2.2.1.内存技术设备,MTD(Memory Technology Device)

MTD,是Linux的存储设备中的一个子系统。其设计此系统的目的是,对于内存类的设备,提供一个抽象层,一个接口,使得对于硬件驱动设计者来说,可以尽量少的去关心存储格式,比如FTL,FFS2等,而只需要去提供最简单的底层硬件设备的读/写/擦除函数就可以了。而对于数据对于上层使用者来说是如何表示的,硬件驱动设计者可以不关心,而MTD存储设备子系统都帮你做好了。

对于MTD子系统的好处,简单解释就是,他帮助你实现了,很多对于以前或者其他系统来说,本来也是你驱动设计者要去实现的很多功能。换句话说,有了MTD,使得你设计Nand Flash的驱动,所要做的事情,要少很多很多,因为大部分工作,都由MTD帮你做好了。

当然,这个好处的一个“副作用”就是,使得我们不了解的人去理解整个Linux驱动架构,以及MTD,变得更加复杂。但是,总的说,觉得是利远远大于弊,否则,就不仅需要你理解,而且还是做更多的工作,实现更多的功能了。

此外,还有一个重要的原因,那就是,前面提到的Nand Flash和普通硬盘等设备的特殊性:

有限的通过出复用来实现输入输出命令和地址/数据等的IO接口,最小单位是页而不是常见的bit,写前需擦除等,导致了这类设备,不能像平常对待硬盘等操作一样去操作,只能采取一些特殊方法,这就诞生了MTD设备的统一抽象层。

MTD,将Nand Flash,nor flash和其他类型的flash等设备,统一抽象成MTD设备来管理,根据这些设备的特点,上层实现了常见的操作函数封装,底层具体的内部实现,就需要驱动设计者自己来实现了。具体的内部硬件设备的读/写/擦除函数,那就是你必须实现的了。

图表 12 MTD设备和硬盘设备之间的区别

HARD drives | MTD device |

连续的扇区 | 连续的可擦除块 |

扇区都很小(512B,1024B) | 可擦除块比较大 (32KB,128KB) |

主要通过两个操作对其维护操作:读扇区,写扇区 | 主要通过三个操作对其维护操作:从擦除块中读,写入擦除块,擦写可擦除块 |

坏快被重新映射,并且被硬件隐藏起来了(至少是在如今常见的LBA硬盘设备中是如此) | 坏的可擦除块没有被隐藏,软件中要处理对应的坏块问题。 |

HDD扇区没有擦写寿命超出的问题。 | 可擦除块是有擦除次数限制的,大概是104-105次. |

多说一句,关于MTD更多的内容,感兴趣的,去附录中的MTD的主页去看。

关于mtd设备驱动,感兴趣的可以去参考附录中MTD设备的文章,该文章是比较详细地介绍了整个MTD框架和流程,方便大家理解整个mtd框架和Nand Flash驱动。

2.2.2.读操作的硬件到软件的映射

下面这部分主要介绍一下,关于硬件的设计和规范,是如何映射到具体的软件实现的,看了这部分内容之后,你对如何根据硬件的规范去用软件代码实现对应的功能,就有了大概的了解了,然后去实现对应的某硬件的驱动,就有了大概的脉络了。

关于硬件部分的细节,前面其实已经介绍过了,但是为了方便说明,此处还是以读操作为例去讲解硬件到软件是如何映射的。

再次贴出上面的那个图:

图表 13 Nand Flash数据读取操作的时序图

对于上面的从①到⑥,每个阶段所表示的含义,再简单解释一下:

①:此阶段,是读命令第一个周期,发送的命令为0x00。

②:此阶段,依次发送列地址,关于这些行地址,列地址等是如何计算出来的,后面的内容会有详细解释。

③:此阶段是发送对应的行地址

④:此阶段是发送读命令第二周期2nd cycle所对应的命令,0x30

⑤:此阶段是等待时间,等待Nand Flash硬件上准备好对应的数据,以便后续读出。

⑥:此阶段,就是一点点地把所需要的数据读出来。

上面的是内容,说的是硬件是如何设计的,而这硬件的设计,即硬件的逻辑时序是如何规定的,对应的软件实现,也就要如何实现。不过可以看出的是,其中很多步骤,比如步骤1和步骤4,那都是固定的,而且,即使其中的步骤2和步骤3,即使是不同厂家和不同的Nand Flash芯片,除了要写入的列地址和行地址可能不同之外,也都是逻辑一样的,同样地,步骤5和6,也都是一样的,唯一不同的,是每家不同的Nand Flash控制器不同,所以具体到步骤6的时候,去读出数据的方式不同,所以,那一部分肯定是你要实现Nand Flash驱动的时候要自己实现的,而对应的其他几个公有的步骤呢,就有了Linux的MTD层帮你实现好了,所以,下面就来介绍一下,关于读取一个Nand Flash的页Page,Linux的MTD层,是如何具体的帮你实现的:

关于Nand Flash的读操作,即读取一页的数据,这样的读数据的操作,很明显,是从上层文件系统传递过来的,其细节我们在此忽略,但是要知道,上层读取数据的请求,传递到了MTD这一层,其入口是哪个函数,然后我们才能继续往下面分析细节。

关于下面所要的介绍的代码,如果没有明确指出,都是位于此文件:

代码位置: driversmtdnandnand_base.c

MTD读取数据的入口是nand_read,然后调用nand_do_read_ops,此函数主体如下:

static int nand_do_read_ops(struct mtd_info *mtd, loff_t from,

struct mtd_oob_ops *ops)

{

。。。。。。

while(1) {

。。。

/* ㈠:要读取数据,肯定是要先发送对应的读页(read page)的命令 */

chip– >cmdfunc(mtd, NAND_CMD_READ0, 0x00, page);

。。。

/* ㈡:发送完命令,接着就可以去调用read_page函数读取对应的数据了 */

ret = chip– >ecc.read_page(mtd, chip, bufpoi,

buf += bytes;

。。。

readlen – = bytes;

if (! readlen)

break;

/ * For subsequent reads align to page boundary. */

col = 0;

/ * Increment page address */

realpage++;

page = realpage & chip– >pagemask;

。。。

}

。。。

} ? end while 1 ?

。。。。。。

return mtd– >ecc_stats.corrected – stats.corrected ? – EUCLEAN : 0;

} ? end nand_do_read_ops ?

对于上述中步骤㈠的函数cmdfunc,一般来说可以不用自己的驱动中实现,而直接使用MTD层提供的已有的函数,nand_command_lp,其细节如下:

static void nand_command_lp(struct mtd_info *mtd, unsigned int command,

int column, int page_addr)

{

。。。

/ * Command latch cycle */

/* 此处就是就是发送读命令的第一个周期1st Cycle的命令,即0x00,对应着上述步骤中的① */

chip– >cmd_ctrl(mtd, command & 0xff, NAND_NCE | NAND_CLE | NAND_CTRL_CHANGE);

if (column ! = – 1 | | page_addr ! = – 1) {

int ctrl = NAND_CTRL_CHANGE | NAND_NCE | NAND_ALE;

/ * Serially input address */

if (column ! = – 1) {

/ * Adjust columns for 16 bit buswidth */

if (chip– >options & NAND_BUSWIDTH_16)

column >>= 1;

/* 接下来是发送两个column,列地址,对应着上述步骤中的② */

chip– >cmd_ctrl(mtd, column, ctrl);

ctrl &= ~NAND_CTRL_CHANGE;

chip– >cmd_ctrl(mtd, column >> 8, ctrl);

}

if (page_addr ! = – 1) {

/* 然后发送三个row行地址,对应着上述步骤中的③ */

chip– >cmd_ctrl(mtd, page_addr, ctrl);

chip– >cmd_ctrl(mtd, page_addr >> 8, NAND_NCE | NAND_ALE);

/ * One more address cycle for devices > 128MiB */

if (chip– >chipsize > (128 << 20))

chip– >cmd_ctrl(mtd, page_addr >> 16, NAND_NCE | NAND_ALE);

}

} ? end if column! =- 1| | page_addr… ?

chip– >cmd_ctrl(mtd, NAND_CMD_NONE, NAND_NCE | NAND_CTRL_CHANGE);

/ *

* program and erase have their own busy handlers

* status, sequential in, and deplete1 need no delay

*/

switch (command) {

。。。

case NAND_CMD_READ0:

/* 接下来发送读命令的第二个周期2nd Cycle的命令,即0x30,对应着上述步骤中的④ */

chip– >cmd_ctrl(mtd, NAND_CMD_READSTART,

NAND_NCE | NAND_CLE | NAND_CTRL_CHANGE);

chip– >cmd_ctrl(mtd, NAND_CMD_NONE,

NAND_NCE | NAND_CTRL_CHANGE);

/ * This applies to read commands */

default:

。。。

} ? end switch command ?

/ * Apply this short delay always to ensure that we do wait tWB in

* any case on any machine. */

/* 此处是对应着④中的tWB的等待时间*/

ndelay(100);

/* 接下来就是要等待一定的时间,使得Nand Flash硬件上准备好数据,以供你之后读取,即对应着步骤⑤ */

nand_wait_ready(mtd);

} ? end nand_command_lp ?

对于之前的步骤㈡的函数read_page,一般来说也可以不用自己的驱动中实现,而直接使用MTD层提供的已有的函数,nand_read_page_hwecc,该函数所要实现的功能,正是上面余下没介绍的步骤⑥,即一点点的读出我们要的数据:

static int nand_read_page_hwecc(struct mtd_info *mtd, struct nand_chip *chip,

uint8_t *buf, int page)

{

。。。

for (i = 0; eccsteps; eccsteps– – , i += eccbytes, p += eccsize) {

chip– >ecc.hwctl(mtd, NAND_ECC_READ);

/* 真正的数据读取,就是下面这个read_buf函数了 */

chip– >read_buf(mtd, p, eccsize);

chip– >ecc.calculate(mtd, p, &ecc_calc[i]);

}

。。。

} ? end nand_read_page_hwecc ?

上面的read_buf,就是真正的去读取数据的函数了,由于不同的Nand Flash controller控制器所实现的方式不同,所以这个函数必须在你的Nand Flash驱动中实现,即MTD层,能帮我们实现的都实现了,不能实现的,那肯定要你的驱动自己实现。

对于我们这里的s3c2410的例子来说,就是s3c2410_nand_read_buf:

文件位置:driversmtdnands3c2410.c

static void s3c2410_nand_read_buf(struct mtd_info *mtd, u_char *buf, int len)

{

struct nand_chip *this = mtd->priv;

/* 到真正的地址去读取数据 */

readsb(this->IO_ADDR_R, buf, len);

}

可以看出,此处的实现相当地的简单,就是读取对应的IO的地址,然后就可以把数据读出来就可以了。不过,要注意的是,并不是所有的驱动都是这么简单,具体情况则是不同的Nand Flash控制器对应不同实现方法。

至此,关于整个的Nand Flash的读取一页的数据的操作,是如何将硬件的逻辑时序图,映射到对应的软件的实现的,就已经介绍完了。而看懂了这个过程,你才会更加明白,原来MTD层,已经帮助我们实现了很多很多通用的操作所对应的软件部分,而只需要我们实现剩下那些和具体硬件相关的操作的函数,就可以了,可以说大大减轻了驱动开发者的工作量。

因为,如果没了MTD层,那么上面那么多的函数,几乎都要我们自己实现,单单是代码量,就很庞大,而且再加上写完代码后的驱动测试功能是否正常,使得整个驱动开发,变得难的多得多。

2.2.3.Nand flash驱动工作原理

在介绍具体如何写Nand Flash驱动之前,我们先要了解,大概的整个系统,和Nand Flash相关的部分的驱动工作流程,这样,对于后面的驱动实现,才能更加清楚机制,才更容易实现,否则就是,即使写完了代码,也还是没搞懂系统是如何工作的了。

让我们以最常见的,Linux内核中已经有的三星的Nand Flash驱动,来解释Nand Flash驱动具体流程和原理。

此处是参考2.6.29版本的Linux源码中的driversmtdnands3c2410.c,以2410为例。

在Nand Flash驱动加载后,第一步,就是去调用对应的init函数,s3c2410_nand_init,去将在Nand Flash驱动注册到Linux驱动框架中。

驱动本身,真正开始,是从probe函数,s3c2410_nand_probe->s3c24xx_nand_probe,

在probe过程中,去用clk_enable打开Nand Flash控制器的clock时钟,用request_mem_region去申请驱动所需要的一些内存等相关资源。然后,在s3c2410_nand_inithw中,去初始化硬件相关的部分,主要是关于时钟频率的计算,以及启用Nand Flash控制器,使得硬件初始化好了,后面才能正常工作。

需要多解释一下的,是这部分代码:

for (setno = 0; setno < nr_sets; setno++, nmtd++) {

pr_debug(“initialising set %d (%p, info %p)n”, setno, nmtd, info);

/* 调用init chip去挂载你的nand 驱动的底层函数到Nand Flash的结构体中,以及设置对应的ecc mode,挂载ecc相关的函数 */

s3c2410_nand_init_chip(info, nmtd, sets);

/* scan_ident,扫描nand 设备,设置Nand Flash的默认函数,获得物理设备的具体型号以及对应各个特性参数,这部分算出来的一些值,对于Nand Flash来说,是最主要的参数,比如nand falsh的芯片的大小,块大小,页大小等。 */

nmtd->scan_res = nand_scan_ident(&nmtd->mtd,

(sets) ? sets->nr_chips : 1);

if (nmtd->scan_res == 0) {

s3c2410_nand_update_chip(info, nmtd);

/* scan tail,从名字就可以看出来,是扫描的后一阶段,此时,经过前面的scan_ident,我们已经获得对应Nand Flash的硬件的各个参数,然后就可以在scan tail中,根据这些参数,去设置其他一些重要参数,尤其是ecc的layout,即ecc是如何在oob中摆放的,最后,再去进行一些初始化操作,主要是根据你的驱动,如果没有实现一些函数的话,那么就用系统默认的。 */

nand_scan_tail(&nmtd->mtd);

/* add partion,根据你的Nand Flash的分区设置,去分区 */

s3c2410_nand_add_partition(info, nmtd, sets);

}

if (sets != NULL)

sets++;

}

等所有的参数都计算好了,函数都挂载完毕,系统就可以正常工作了。

上层访问你的nand falsh中的数据的时候,通过MTD层,一层层调用,最后调用到你所实现的那些底层访问硬件数据/缓存的函数中。

3. Linux下Nand Flash驱动编写步骤简介

关于上面提到的,在nand_scan_tail的时候,系统会根据你的驱动,如果没有实现一些函数的话,那么就用系统默认的。如果实现了自己的函数,就用你的。

估计很多人就会问了,那么到底我要实现哪些函数呢,而又有哪些是可以不实现,用系统默认的就可以了呢。

此问题的,就是我们下面要介绍的,也就是,你要实现的,你的驱动最少要做哪些工作,才能使整个Nand Flash工作起来。

3.1. 对于驱动框架部分

其实,要了解,关于驱动框架部分,你所要做的事情的话,只要看看三星的整个Nand Flash驱动中的这个结构体,就差不多了:

static struct platform_driver s3c2410_nand_driver = {

.probe = s3c2410_nand_probe,

.remove = s3c2410_nand_remove,

.suspend = s3c24xx_nand_suspend,

.resume = s3c24xx_nand_resume,

.driver = {

.name = “s3c2410-nand”,

.owner = THIS_MODULE,

},

};

对于上面这个结构体,没多少要解释的。从名字,就能看出来:

(1)probe就是系统“探测”,就是前面解释的整个过程,这个过程中的多数步骤,都是和你自己的Nand Flash相关的,尤其是那些硬件初始化部分,是你必须要自己实现的。

(2)remove,就是和probe对应的,“反初始化”相关的动作。主要是释放系统相关资源和关闭硬件的时钟等常见操作了。

(3)suspend和resume,对于很多没用到电源管理的情况下,至少对于我们刚开始写基本的驱动的时候,可以不用关心,放个空函数即可。

3.2. 对于Nand Flash底层操作实现部分

而对于底层硬件操作的有些函数,总体上说,都可以在上面提到的s3c2410_nand_init_chip中找到:

static void s3c2410_nand_init_chip(struct s3c2410_nand_info *info,

struct s3c2410_nand_mtd *nmtd,

struct s3c2410_nand_set *set)

{

struct nand_chip *chip = &nmtd->chip;

void __iomem *regs = info->regs;

chip->write_buf = s3c2410_nand_write_buf;

chip->read_buf = s3c2410_nand_read_buf;

chip->select_chip = s3c2410_nand_select_chip;

chip->chip_delay = 50;

chip->priv = nmtd;

chip->options = 0;

chip->controller = &info->controller;

switch (info->cpu_type) {

case TYPE_S3C2410:

/* Nand Flash控制器中,一般都有对应的数据寄存器,用于给你往里面写数据,表示将要读取或写入多少个字节(byte,u8)/字(word,u32) ,所以,此处,你要给出地址,以便后面的操作所使用 */

chip->IO_ADDR_W = regs + S3C2410_NFDATA;

info->sel_reg = regs + S3C2410_NFCONF;

info->sel_bit = S3C2410_NFCONF_nFCE;

chip->cmd_ctrl = s3c2410_nand_hwcontrol;

chip->dev_ready = s3c2410_nand_devready;

break;

。。。。。。

}

chip->IO_ADDR_R = chip->IO_ADDR_W;

nmtd->info = info;

nmtd->mtd.priv = chip;

nmtd->mtd.owner = THIS_MODULE;

nmtd->set = set;

if (hardware_ecc) {

chip->ecc.calculate = s3c2410_nand_calculate_ecc;

chip->ecc.correct = s3c2410_nand_correct_data;

/* 此处,多数情况下,你所用的Nand Flash的控制器,都是支持硬件ECC的,所以,此处设置硬件ECC(HW_ECC) ,也是充分利用硬件的特性,而如果此处不用硬件去做的ECC的话,那么下面也会去设置成NAND_ECC_SOFT,系统会用默认的软件去做ECC校验,相比之下,比硬件ECC的效率就低很多,而你的Nand Flash的读写,也会相应地要慢不少*/

chip->ecc.mode = NAND_ECC_HW;

switch (info->cpu_type) {

case TYPE_S3C2410:

chip->ecc.hwctl = s3c2410_nand_enable_hwecc;

chip->ecc.calculate = s3c2410_nand_calculate_ecc;

break;

。。。。。

}

} else {

chip->ecc.mode = NAND_ECC_SOFT;

}

if (set->ecc_layout != NULL)

chip->ecc.layout = set->ecc_layout;

if (set->disable_ecc)

chip->ecc.mode = NAND_ECC_NONE;

}

而我们要实现的底层函数,也就是上面蓝色标出来的一些函数而已:

(1)s3c2410_nand_write_buf 和 s3c2410_nand_read_buf:这是两个最基本的操作函数,其功能,就是往你的Nand Flash的控制器中的FIFO读写数据。一般情况下,是MTD上层的操作,比如要读取一页的数据,那么在发送完相关的读命令和等待时间之后,就会调用到你底层的read_buf,去Nand Flash的FIFO中,一点点把我们要的数据,读取出来,放到我们制定的内存的缓存中去。写操作也是类似,将我们内存中的数据,写到Nand Flash的FIFO中去。

(2)s3c2410_nand_select_chip : 实现Nand Flash的片选。

(3)s3c2410_nand_hwcontrol:给底层发送命令或地址,或者设置具体操作的模式,都是通过此函数。

(4)s3c2410_nand_devready:Nand Flash的一些操作,比如读一页数据,写入(编程)一页数据,擦除一个块,都是需要一定时间的,在命发送完成后,就是硬件开始忙着工作的时候了,而硬件什么时候完成这些操作,什么时候不忙了,变就绪了,就是通过这个函数去检查状态的。一般具体实现都是去读硬件的一个状态寄存器,其中某一位是否是1,对应着是出于“就绪/不忙”还是“忙”的状态。这个寄存器,也就是我们前面分析时序图中的R/B#。

(5)s3c2410_nand_enable_hwecc: 在硬件支持的前提下,前面设置了硬件ECC的话,要实现这个函数,用于每次在读写操作前,通过设置对应的硬件寄存器的某些位,使得启用硬件ECC,这样在读写操作完成后,就可以去读取硬件校验产生出来的ECC数值了。

(6)s3c2410_nand_calculate_ecc:如果是上面提到的硬件ECC的话,就不用我们用软件去实现校验算法了,而是直接去读取硬件产生的ECC数值就可以了。

(7)s3c2410_nand_correct_data:当实际操作过程中,读取出来的数据所对应的硬件或软件计算出来的ECC,和从oob中读出来的ECC不一样的时候,就是说明数据有误了,就需要调用此函数去纠正错误。对于现在SLC常见的ECC算法来说,可以发现2位,纠正1位。如果错误大于1位,那么就无法纠正回来了。一般情况下,出错超过1位的,好像几率不大。至少我看到的不是很大。更复杂的情况和更加注重数据安全的情况下,一般是需要另外实现更高效和检错和纠错能力更强的ECC算法的。

当然,除了这些你必须实现的函数之外,在你更加熟悉整个框架之后,你可以根据你自己的Nand Flash的特点,去实现其他一些原先用系统默认但是效率不高的函数,而用自己的更高效率的函数替代他们,以提升你的Nand Flash的整体性能和效率。

4. 引用文章

http://hi.baidu.com/serial_story/blog/item/3f1635d1dc041cd7562c84a1.html

2. Samsung的型号为K9G8G08U0M的Nand Flash的数据手册

要下载数据手册,可以去这里介绍的网站下载:

samsung 4K pagesize SLC Nand Flash K9F8G08U0M datasheet + 推荐一个datasheet搜索的网站

http://hi.baidu.com/serial_story/blog/item/7f25a03def1de309bba167c8.html

http://hi.baidu.com/serial_story/blog/item/f06db3546eced11a3b29356c.html

4. Memory Technology Device (MTD) Subsystem for Linux.

http://www.linux-mtd.infradead.org/index.html

5. NAND和NOR的比较

http://hi.baidu.com/serial_story/blog/item/c669991efe491e1b403417e5.html

http://www.cnitblog.com/luofuchong/archive/2007/08/31/32682.html

http://www.cnitblog.com/luofuchong/archive/2007/09/04/32939.html

7. 芯片内执行(XIP, eXecute In Place):

http://hi.baidu.com/serial_story/blog/item/adb20a2a3f8ffe3c5243c1df.html