相关内容:

SDRAM内存中的重要参数解析

关于BRC和RBC:

【详解】SDRAM的地址映射方式BRC(Bank Row Column)和RBC(Row Bank Column)

其中,那个截图,参考的是:

An Introduction to SDRAM and memory controllers – Benny Akesson

其中,核心就只有一句:

BRC==B-R-C (Bank, Row, Column)

RBC==R-B-C (Row, Bank, Column)

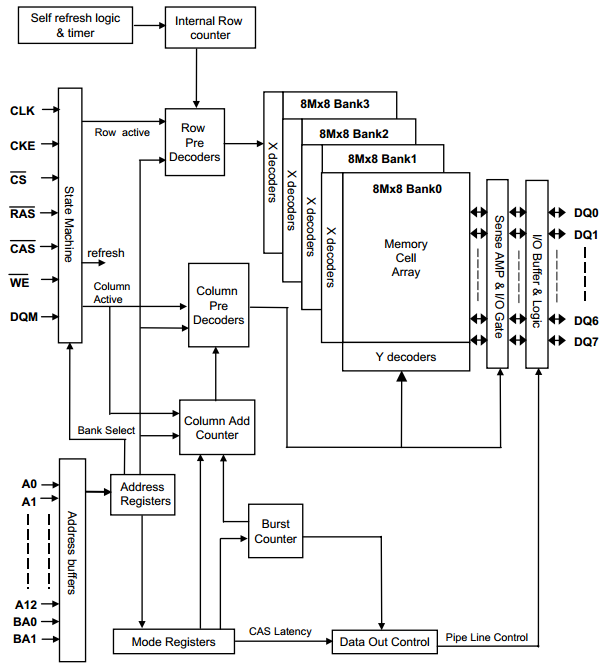

SDRAM内存的内部物理层次和结构

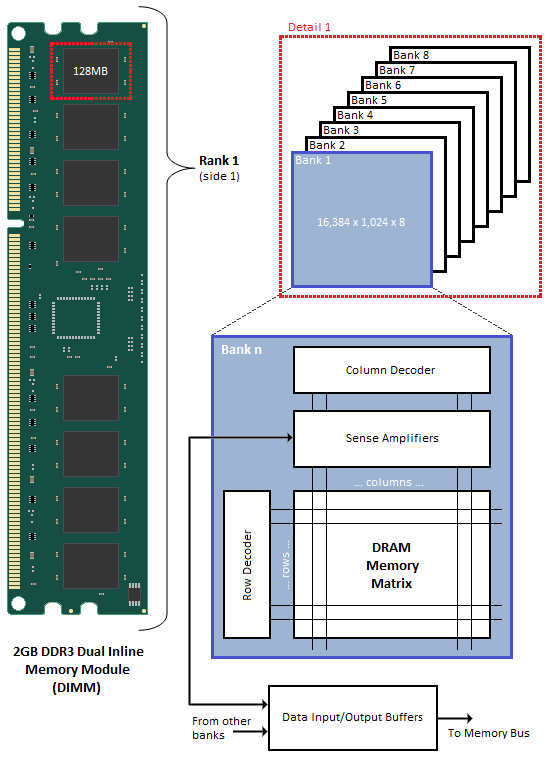

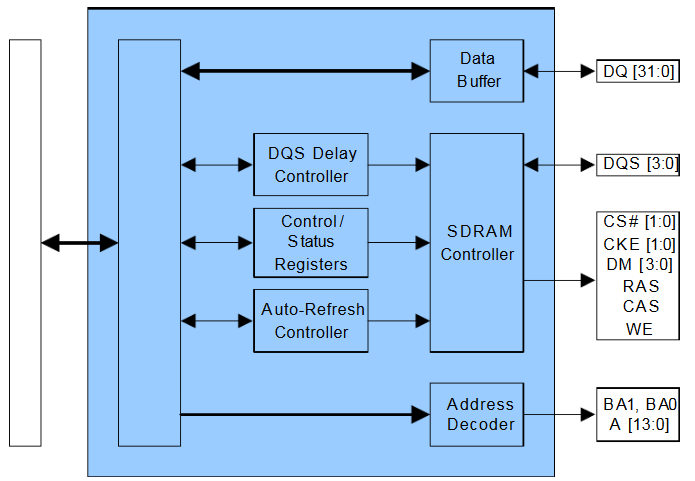

如图:

其中,很明显是:

上图中的DRAM Memory Matrix中的:

- rows,对应的长度是上面的那个16384==16K

- columns,对应的长度是上面的那个1024==1K

- 对应的行和列交叉的点,对应的大小是8bit==1Byte

SDRAM内存中的bank

对应的bank,就是上述上面这个单根内存。

而在一般PC上,台式机中,对应的是主板上的内存的多个插槽

比如:

就是有6个插槽,就是6个bank

上面插了6个内存条。

SDRAM内存的单个bank的容量大小计算方法

所以,上述例子中的bank的计算方法就是:

单个bank的大小 == row address width * column address width * memory data width == rows number * columns number * memory data width == 16K * 1K * 1Byte ==16MBytes ==16MB |

相应的的解释:

Typical figures: 4-8 banks 16K rows/bank 1024 columns/row 4-16 bits/column |

的含义就是:

此处这个单个bank是16MB的内存:

如图,一共:

8个bank,每个bank是上面算出来的是16MB

16384==16K rows/bank 1024==1K columns/row 8bits/column |

所以,此处,总的内存容量是:

16MB*8=128MB

了。

嵌入式驱动中如何写代码去配置对应的SDRAM内存

明白如何计算SDRAM内存的row address width和column address number

即,内存的容量计算,所对应的嵌入式中的内存驱动方面的代码,如何写。

关于内存容量,按照上面的例子,是:

bank number * size per bank == bank number * (rows number/bank * columns number/row * bits/column) == 8 * (16K * 1K * 8) == 1024MBits == 128MBytes |

需要注意的是:

在写SDRAM驱动时,往往,上面的

- rows number/bank==16K

- columns number==1K

不是直接写成16K和1K的。

而是:

有个对应的:

- row address width

- column address number

此处,其值就是:

- row address width == 2的次方数,而16K是2的14次方

- 所以此处:

- row address width ==14

同理:

- column address number == 2的次方数 而1K是2的10次方,

- 所以此处是:

- column address number == 10

类似的,之前见过的,某个MPMC(参见附录的解释)

找到SDRAM内存的数据手册中的详细参数

驱动中,去配置MT48LC32M16A2内存时,其配置是:

1 2 3 4 | #define MT48LC32M16A2_SIZEMB 64 /*!< memory size in MBytes*/#define MT48LC32M16A2_SIZEBYTES (64 * 1024 * 1024)#define MT48LC32M16A2_CLMN_ADDR_WIDTH 10#define MT48LC32M16A2_ROW_ADDR_WIDTH 13 |

其中的很容易看出:

这个MT48LC32M16A2,共64MB

注:此处隐含的条件是:memory data width是8bit=1Byte

对应的datasheet中是:

MT48LC32M16A2 – 8 Meg x 16 x 4 banks

即:

每个bank是8MBit

然后memory data width是16bit

然后一共有4个bank

所以,此处,先算总大小是:

8MBit * 16bit * 4

== 8Mbit * 2Byte * 4

== 64MB

搞懂代码中如何配置SDRAM内存的参数

然后,再去看看,上面的:

MT48LC32M16A2_CLMN_ADDR_WIDTH为何设置为10

MT48LC32M16A2_ROW_ADDR_WIDTH为何设置为13

那是因为:

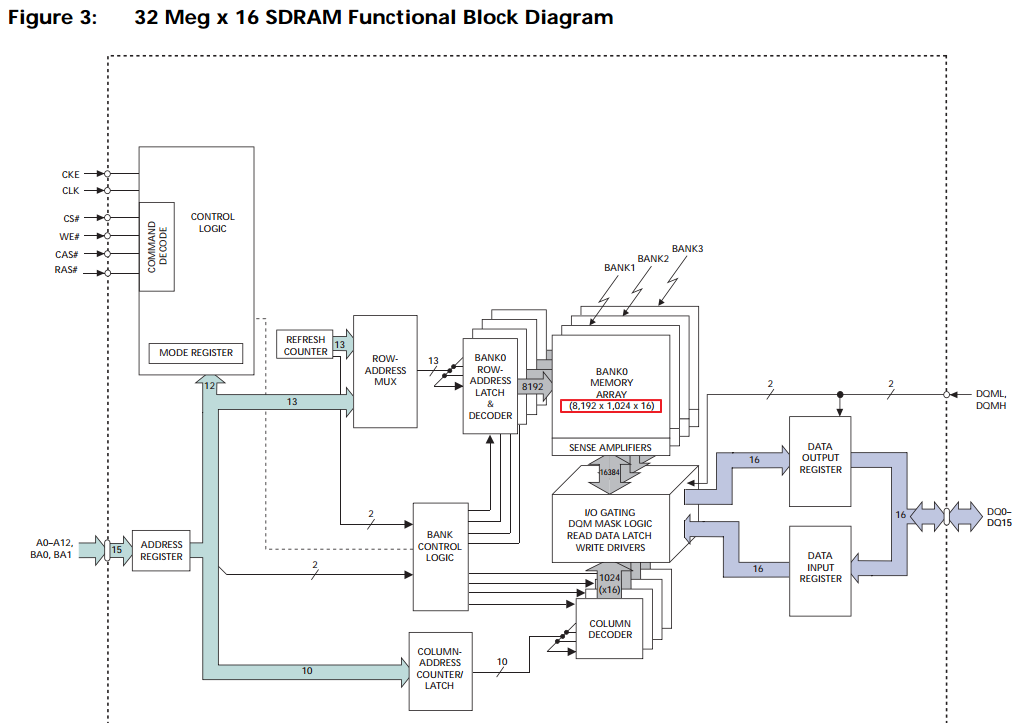

先去看其datasheet中的图示:

注意,是”32 Meg x 16 SDRAM“,对应的这个图:

其中可见:

每个bank是:

8,192×1,024×16

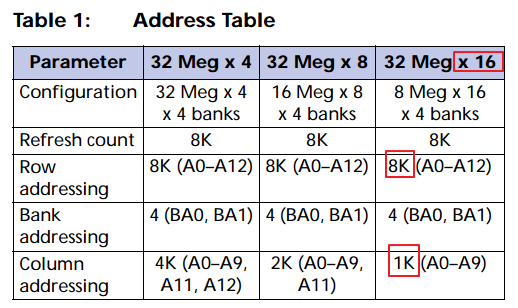

其实,8192,1024,16,这几个参数,也可以在datasheet中的表格中看到:

即:

表格中也写了,对于:

32Megx16,说明是x16,即16bit的

对应的:

row addressing是8K==8192

column addressing是1K==1024

然后再去推算:

MT48LC32M16A2_CLMN_ADDR_WIDTH

== row address width

== row个数对应的是2的多少次方

== 此处column个数是1024

== 1024是2的10次方

== 10

所以,此处配置为:

1 | #define MT48LC32M16A2_CLMN_ADDR_WIDTH 10 |

MT48LC32M16A2_ROW_ADDR_WIDTH

== column address width

== column个数对应的是2的多少次方

== 此处column个数是8192

== 8192是2的13次方

== 13

所以,此处配置为:

1 | #define MT48LC32M16A2_ROW_ADDR_WIDTH 13 |

关于SDRAM内存数据宽度的写法和引用

其中的:

memory data width

内存数据宽度

对应的单位是bit,通常也写成xN

常见都有:

4bit==x4

8bit==x8

x16==x16

对应的图表中的写法,是那个DQ。

比如:

中的:

DQ[31:0]

表示:

此处的内存数据宽度是0-31,供32位,即32bit==4Byte

按照之前的那个算法:

如果前面的Bank中,内存数据宽度,不是那个8==8bit,而是此处的32bit==4Byte的话,那么上面的内存,单个的bank的大小就是:

16,384×1,024x32bit

== 16K x 1K x 4Byte

== 64MB

了。

更多的SDRAM内存的内部结构的例子

再给出另外两个内存的架构的例子:

HY57V56820C(L)T内部结构图

可见,其中是:

DQ是:

DQ[7:0]

即:

0-7,共8位的DQ

即:

memory data width 内存数据宽度

为8bit。

如此,才算,真正搞懂了,

内存的

bank

row

column

memory data width

的含义,以及拿到一个内存,去看对应的datasheet,如何去写其驱动,如何设置对应的

row address width

column address width

等参数,如何计算内存的总容量了。

其他一些SDRAM内存控制器

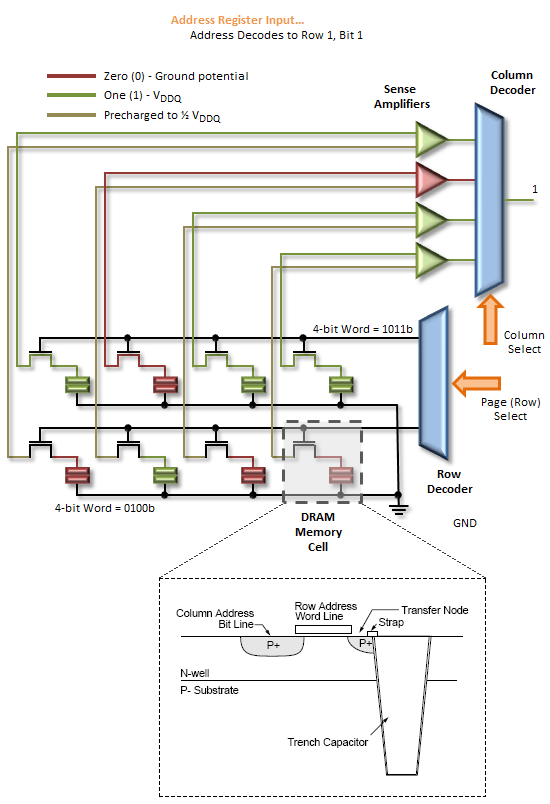

继续深入了解SDRAM内存单元结构和原理

后续再深入了解内部机制:

表示的是:

是x4==4bit==内存位宽是4bit

的内存的例子。

每次,访问row和column的交叉点,即对应的单个的cell

然后读取出对应的值。

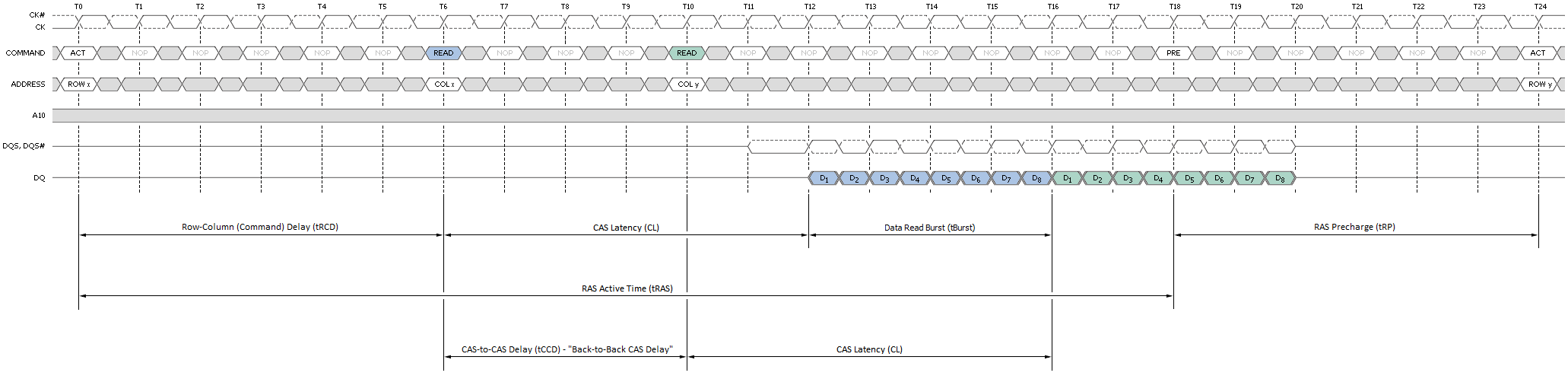

对应的物理上的时序图,就是:

至此,才算是,对于SDRAM的结构,更加有个了解了。

参考资料

【详解】SDRAM的地址映射方式BRC(Bank Row Column)和RBC(Row Bank Column)

An Introduction to SDRAM and memory controllers – Benny Akesson

Everything You Always Wanted to Know About SDRAM (Memory): But Were Afraid to Ask – A Break from the Norm

Micron的MT48LC32M16A2的datasheet

HY5756820C : 4 Banks x 8M x 8Bit Synchronous DRAM Hynix Semiconductor

附录

MPMC

1.MPMC==Multiport Memory Controller==多端口存储设备控制器

参考自:

Tutorial 1:Sharing DRAM between Modules Using MPMC

2.而:

LogiCORE IP Multi-Port Memory Controller, MPMC (v6.03.a) – mpmc.pdf

中更详细的解释:

”MPMC is a fully parameterizable memory controller that supports SDRAM/DDR/DDR2/DDR3/LPDDR memory.“

即:

MPMC是一个内存控制器,可以通过参数配置以支持各种不同类型的存储器:SDRAM/DDR/DDR2/DDR3/LPDDR内存

转载请注明:在路上 » 【整理】详解嵌入式片上资源之SDRAM内存